靜電放電(ESD)會給電子器件環境會帶來破壞性的后果。事實上,在各種各樣電路的電路封裝和經過裝配、正在使用大電子器件中,超過25%的半導體芯片損壞歸咎于ESD。

通常情況下,來自人體某個部分(手指)的放電將給給不同的材料充電,隨后傳遞到附著在電子器件的導電觸點。這將造成IC損壞,并有理由指責終端用戶器件制造商。

這個問題非常嚴重,以至于歐盟(European Union)已經為任何在經濟區銷售的商品制定了特殊的ESD抑制標準。現在設計工程師必須為當今更敏感的半導體提供有效的ESD保護。

不幸地是,這項任務經常遵循事后回想的設計原則:首先搭建沒有額外過壓瞬間抑制的電路,依靠板上的IC來進行保護。如果測試能顯示在原型階段的靈敏度,那么就加上保護器件。如果這種方法被采用來滿足當今更低放大電壓,增加頻率和更低噪聲的要求的話,整個設計必須最優的并是集成的。在末端增加保護可能非常昂貴,或由于時間限制而不切實際。

通常,ESD事件是由根據充電過程類型和瞬態電泳嚴重程度的三種主要ESD算法描述的:人體模型(HBM)、充電器件模型(CDM)和機器模型(MM)。這些模型定義了瞬變效應的類型,因此設計工程師們就可以定義明確的半導體過壓芯片瞬變等級靈敏度,以及芯片及裝配產品測試規程。利用這些模型,電路設計工程師可以測試芯片和產品的ESD保護效率相一致,而且可以定量地與可選方案進行比較。

電荷通過一系列電阻器直接傳遞,例如人的手指,是最普遍的ESD損壞原因。因此,優秀的ESD模型是HBM。在測試中待測器件中(DUT),這是由一個100pF的電容通過一個1500Ω的電阻向器件放電來表示的。這個標準的商業版本是軍用規范883方法3015(圖1a)。

最流行的HBM變種是國際電工委員會IEC1000-4-2標準,定義為150pF電容通過一個330Ω電阻放電(圖1b)。這是歐盟對在其區域內商品銷售所必須的國際測試。#p#分頁標題#e#

但是,明顯的瞬間電壓威脅和能量等級的不同存在于兩個模型之中。于是設計工程師可以使測試過程適合他們所期望的具體應用。例如,IEC1000-4-2具有一個非常快速的電平脈沖上升時間,能應用更多的脈沖和更高的峰值電流(見表格)。

最近,電路設計工程師已經正在通過一定數量的瞬間電壓抑制器(TVS)器件增加保護。一些例子包括固狀器件(二極管)、金屬氧化物變阻器(MOV)、可控硅整流器、其他可變電壓的材料(新聚合物器件)、氣體電子管和簡單的火花隙。

這類器件被放置在輸入端和地之間。當輸入電壓達到引起它們“開路”或導通的水平時,它們能迅速把阻抗降低。理想地,輸入威脅被部分地反射回去,而平衡被部分地通過導通的TVS器件分流到地上。所以,在電路中只有更小比例的威脅能夠達到敏感的IC。

但是ESD抑制器件也有著其自身的優缺點,隨著新一代高速電路的出現,一些缺點被放大了。例如,TVS必須迅速響應到來的浪涌電壓。浪涌電壓在0.7ns達到8KV(或更高)峰值時,TVS器件的觸發或調整電壓(與輸入線平行)必須要足夠低以便作為一個有效的電壓分配器。

一些器件可保護電路,但在僅幾次電流脈沖和/或陷入進入低阻(短路)狀態后就老化了,形成電路到地的大電電流通道。這點對由電池驅動的器件來說是致命的。

每個器件有其自身的差異。氣體放電管可通過大電流,但是響應速度很慢。它們也會老化且不能恢復。MOV能為高速電路提供相對緩慢的導通響應。硅二極管的觸發響應速度非常快,導通電壓低,但它們像MOVS和其他器件一樣,電容比較高,從而影響高速信號。

頻率越高,電容效應就越大。全新的ESD變壓器件是當前僅有能夠提供極低電容和非常低關斷漏電流的產品。此外,在多次脈沖之后它們能自我恢復。

現在考慮成本因素。設計工程師盡可能地把非主要器件的成本降到最低。由于供大于求,二極管的價格一直以來都很低。一些新的高頻聚合物器件的價格也十分有競爭力。#p#分頁標題#e#

過去幾個主要的設計因素簡化了ESD抑制器問題。工作電壓更高、速度更慢、更魯棒的IC對浪涌電壓不那么敏感。更低的工作頻率也意味著保護速度不那么重要。同時,阻抗更高線路和引腳元件的電路、金屬更多的封裝以及更少的外部節點,也使事情變得更加簡單。

但是電子行業已發生變化。消費電信行業在發生爆炸式發展,出現了更多的手持設備。器件的工作頻率已經從幾kHz上升到GHz,從而使用于ESD保護的高容量無源器件帶來設計失真問題。此外,芯片工作電壓正在降低,有助于極大提高對任和高能量瞬態(固定結點的加熱/融化)響應的靈敏度。同時,新型高頻數碼使用器件要求關斷漏電流非常低,從而降低噪聲。

在低成本的生產環境中,對于所有的電路元件來說降低成本是主要目標。因此,有效的ESD抑制器應為設計工程師提供下列主要的好處和特點(未必按重要性排列):

具有成本效益;

保護新型消費電子的音頻和視頻I/O線路以及RF連接端口,而無需犧牲性能;

保護新型通信連接硬件;

在很廣的工作頻率范圍內具有穩定的器件特性;

在工作頻率為數GHz的超寬帶電路中采用1pF以下的電容;

在關狀態條件下漏電流最小,以減小噪音;

降低由ESD抑制器元件引起的工作電路信號失真和減衰;

為提供有效保護,觸發和箝位特性要與電路器件要求一致;

具有所需的裝配特性、外形因子和#p#分頁標題#e#PCB封裝,便于用在高速自動裝配生產線上;

在各種可選擇的器件中,最好是在無需改變電路板的情況下具有高互換性;

在產品使用壽命期間可靠性高。

布局指南

不管選擇怎樣的TVS器件,它們在電路板上的布局非常重要。TVS布局前的導線長度應該減到最小,因為快速(0.7ns)ESD脈沖可能產生導致TVS保護能力下降的額外電壓。

另外,快速ESD脈沖可能在電路板上相鄰(平行)導線間產生感應電壓。如果上述情況發生,由于將不會得到保護,因為感應電壓路徑將成為另一條讓浪涌到達IC的路徑。因此,被保護的輸入線不應該被放置在其它單獨、未受保護的走線旁邊。推薦的ESD抑制器件PCB布局方案應該是:放置在被保護的IC之前,但盡量與連接器/觸點PCB側盡量近這; 放置在與信號線串聯任何電阻之前; 放置在包含保險絲在內的過濾或調節器件之前; 放置在IC之前的其他可能有ESD的地方。

由于業界對在高頻電路中采用ESD抑制越來越感興趣,所以已對消費電子領域中的一些大型器件進行了研究。對比數據表明,盡管低成本的硅二極管(甚至變阻器)的觸發/箝位電壓非常低,但它們的高頻容量和漏電流無法滿足不斷增長的應用需求。

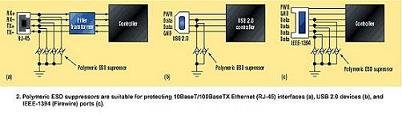

另一個重要要求是ESD抑制器對電路信號特性的影響最小。對聚合物ESD抑制器的測量表明,頻率高達6GHz時的衰減小于0.2dB,這樣它們對電路幾乎沒有影響。

#p#分頁標題#e#

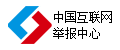

另外,商業化產品要求在所有不同的硬件接口位置都要有ESD浪涌保護。例如,一些新型電腦和更高端的消費電子可能會如下這些互連器件的大部分或者全部:以太網、USB1.1/USB2.0、IEEE-1394/1394b、音頻/視頻/RF以及傳統的RS-232、RJ-11等端口等的audio/video/RF端口。所有傳統的保護器件都已經不同程度地得以成功應用。但是,如今不斷增長的工作頻率為超低電容器件(如聚合物抑制器)提出了需求。

USB 2.0 協議具有00 Mbps的快速數據轉換速率。因此,當采用具有SurgX技術的超低電容聚合物器件進行保護時,一個配備了USB 2.0功能的器件將具有最佳性能。這將比使用齊納二極管或多層變阻器時產生更少的數據失真。

另外,許多新型消費電子器件能執行快速的IEEE-1394/1394b(Fireware)數據轉換協議。這種非常高的數據速率(1600 Mbps,1394b)要求低電容ESD抑制器,例如聚合物浪涌器件。測試數據表明,聚合物ESD抑制器帶來的信號失真比硅二極管器件保護Firewire端口產生的更少。

轉載請注明出處。

相關文章

相關文章

熱門資訊

熱門資訊

精彩導讀

精彩導讀

關注我們

關注我們